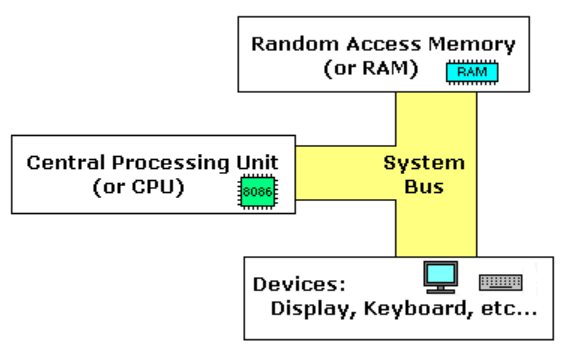

In computer architecture, a bus is a communication system that transfers data between components inside a computer or between computers. It consists of a set of parallel wires (or traces) that carry data, addresses, and control signals. Buses are used to connect various components of a computer system, allowing them to communicate with each other.

What is a Bus?

A bus refers to a communication pathway or set of wires that allows different components within a computer system to transfer data and signals between each other. Buses serve as the central nervous system of a computer, facilitating communication between the CPU (Central Processing Unit), memory, peripherals, and other hardware components.

System Bus:

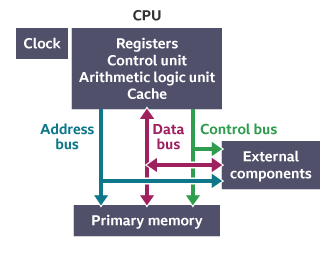

A system bus is a collection of buses that connects the CPU (Central Processing Unit), memory, and other major components of a computer system. It serves as the primary communication pathway within a computer, facilitating the transfer of data, addresses, and control signals between the CPU and other devices. The system bus is also sometimes referred to as the front-side bus (FSB) or the host bus.

The system bus typically consists of three main types of buses:

- Address Bus

- Data Bus

- Control Bus

1 Address Bus:

The address bus is a unidirectional bus in a computer system that carries memory addresses from the CPU (Central Processing Unit) to memory and other devices. It is one of the main components of the system bus and is responsible for specifying the memory location that the CPU wants to read from or write to.

Here are the key characteristics of the address bus:

Unidirectional:

- The address bus carries signals only from the CPU to memory and other devices.

- It is used by the CPU to specify memory addresses for read and write operations.

Width:

- The width of the address bus determines the maximum memory capacity that can be addressed by the CPU i.e., physical memory addressable by the processor.

- It is measured in bits, and the number of bits in the address bus determines the maximum number of memory locations that can be addressed.

- For example, a 32-bit address bus can address

2^32memory locations, which is 4 gigabytes (GB) of memory.

Memory Addressing:

- The CPU generates memory addresses and sends them over the address bus to memory and other devices.

- Memory addresses specify the location of data or instructions in memory.

- The memory controller uses the memory address to access the corresponding memory location and retrieve or store data.

Maximum Addressable Memory:

- The maximum amount of memory that can be addressed by the CPU is determined by the width of the address bus.

- For example, a 32-bit address bus can address up to 4 GB of memory, while a 64-bit address bus can address up to 16 exabytes (EB) of memory.

Controlled by Memory Controller:

- The memory controller is responsible for managing the flow of data between the CPU and memory.

- It interprets the memory addresses sent by the CPU and accesses the corresponding memory locations.

The address bus, along with the data bus and control bus, forms the system bus, which provides a communication pathway for data and instructions between the CPU and other components of the computer system. It plays a crucial role in enabling the CPU to access memory, execute instructions, and interact with the rest of the computer system.

2 Data Bus

The data bus is a bidirectional bus in a computer system that carries data between the CPU (Central Processing Unit), memory, and other devices. It is one of the main components of the system bus and is responsible for transferring data in both directions - from the CPU to memory/devices (write operation) and from memory/devices to the CPU (read operation).

Here are the key characteristics of the data bus:

Bidirectional:

- The data bus carries data in both directions - from the CPU to memory/devices (write operation) and from memory/devices to the CPU (read operation).

- It allows data to be transferred between the CPU and memory/devices for processing and storage.

Width:

- The width of a data bus refers to the number of bits (electrical wires) that the bus can carry at a time.

- Each line carries 1 bit at a time. So, the number of lines in data bus determine how many bits can be transferred parallely.

- The width of the data bus determines the maximum amount of data that can be transferred in a single operation.

- It is measured in bits, and the number of bits in the data bus determines the width of the data path.

- For example, a 32-bit data bus can transfer 32 bits (4 bytes) of data at a time, while a 64-bit data bus can transfer 64 bits (8 bytes) of data at a time.

Data Transfer:

- During a read operation, data is transferred from memory/devices to the CPU over the data bus.

- During a write operation, data is transferred from the CPU to memory/devices over the data bus.

- The CPU uses memory addresses to specify the location of data to be read from or written to.

Synchronous or Asynchronous:

- Data transfer on the data bus can be synchronous or asynchronous, depending on the system architecture.

- In synchronous systems, data transfer is synchronized with a system clock, ensuring that data is transferred at regular intervals.

- In asynchronous systems, data transfer is not synchronized with a system clock, and data is transferred as needed.

Controlled by Memory Controller:

- The memory controller is responsible for managing the flow of data between the CPU and memory/devices.

- It controls data transfer on the data bus, ensuring that data is transferred correctly and efficiently.

3 Control Bus

The control bus is a set of wires in a computer system that carries control signals between the CPU (Central Processing Unit), memory, and other devices. It is one of the main components of the system bus and is responsible for governing the operation of devices and communication between components.

Here are the key characteristics of the control bus:

Control Signals:

- The control bus carries control signals that coordinate the operation of devices and communication between components.

- Control signals include signals for reading from and writing to memory, interrupt requests, clock signals, and bus arbitration signals.

Unidirectional or Bidirectional:

- Control signals on the control bus can be unidirectional (from the CPU to other devices) or bidirectional (in both directions).

- Some control signals, such as clock signals, are typically unidirectional, while others, such as interrupt request signals, may be bidirectional.

Types of Control Signals:

- Memory Read (RD): Indicates that the CPU is requesting data from memory.

- Memory Write (WR): Indicates that the CPU is writing data to memory.

- Input/Output Read (IOR): Indicates that the CPU is requesting data from an I/O device.

- Input/Output Write (IOW): Indicates that the CPU is writing data to an I/O device.

- Interrupt Request (IRQ): Indicates that an I/O device or peripheral is requesting attention from the CPU.

- Clock (CLK): Provides timing signals to synchronize the operation of devices.

- Bus Arbitration Signals: Manage access to the bus in systems with multiple devices sharing the same bus.

Timing and Synchronization:

- Control signals on the control bus are used to synchronize the operation of devices and ensure that data is transferred correctly and efficiently.

- Timing signals, such as clock signals, ensure that devices operate at the correct speed and that data is transferred at the right time.

Controlled by Control Unit:

- The control unit in the CPU is responsible for generating control signals and coordinating the operation of devices and communication between components.

- It interprets instructions and generates the appropriate control signals to carry out those instructions.

Leave a comment

Your email address will not be published. Required fields are marked *